Obvody rozhraní TWO WIRE

Něco málo o sběrnici TWO WIRE

Společnost Atmel zavedla sběrnici TWO WIRE, která je plně kompaktibilní se sběrnicí společnosti Philips označovanou jako I²C. Protože sběrnici I²C můžeme považovat za standard a sběrnici TWO WIRE za její klon, budeme se dále zabývat popisem sběrnice I²C.

Označení sběrnice I²C vychází ze zkratky IIC bus, což můžeme anglicky rozvést jako Internal-Integrated-Circuit Bus. Z názvu lze vydedukovat, že se jedná se o interní datovou sběrnici, která sloužící pro komunikaci a přenos dat mezi propojenými integrovanými obvody téhož zařízení. V současnosti tuto sběrnici podporuje řada integrovaných obvodů nejen firmy Philips. Jedná se především o mikrořadiče, sériové paměti, LCD zobrazovače, audio a video obvody, a/d a d/a převodníky a některé další digitálně řízené obvody. Hlavní výhoda spočívá v nízkém počtu vodičů sběrnice a jejím obousměrném přenosu. Přenos je po dvou vodičích - "data SDA (serial data)"

a "hodiny SCL (serial clock)". To především u mikrokontrolérů výrazně optimalizuje nároky na počet vstupně-výstupních pinů a celkově zjednodušuje výsledné zapojení. Na jednu sběrnici může být připojeno více integrovaných obvodů. V základní verzi jsou obvody adresovány 7bitově a v rozšířené verzi 10bitově. To umožňuje připojení 128 respektive 1024 čipů s různou adresou na jednu společnou sběrnici. V praxi jsou tato čísla však podstatně nižší, protože adresa čipu většinou nelze určit plnými 7 (10) bity ale třeba jen třemi. Někdy nelze určit vůbec a je dána na pevno pro daný typ čipu - takových čipů tedy na jedné sběrnici nemůže být více než jeden. Přenosová rychlost sběrnice je pro většinu aplikací dostatečná i v základní verzi, kde je frekvence hodin 100kHz. Ve vylepšených verzích to může být 400kHz nebo 1MHz, ale ne všechny intergované obvody tuto verzi podporují. Rychlost přenosu pak musí být přizpůsobena pochopitelně "nejpomalejšímu" čipu na sběrnici. Oba vodiče musí být implicitně

v logické jedničce a to je zajištěno pull-up rezistory. Jejich odpory mají hodnotu v řádech jednotek kiloohmů. Čím je vyšší komunikační frekvence, tím musí být nižší hodnoty těchto odporů. Pro 100kHz postačuje hodnota rezistorů 4k7.

Popis sběrnice a komunikace

Sběrnice je tvořena dvojicí vodičů, na kterých je v klidovém stavu zvyšovacími odporyudržována kladná hodnota napětí. Tyto vodiče sběrnice mají označení SCL a SDA. Na vodiči sběrnice SCL jsou synchronizační hodinové impulzy pro sériový přenos datových impulsů na sběrnicovém vodiči SDA. Budiče sběrnice připojených obvodů k této sběrnici pracují v zapojení s otevřeným kolektorem, aby sběrnice byla využívána skupinou rovnoprávných řadičů.

Obr. 1: Blokové schéma obvodů připojení na sběrnici I2C

Komunikaci zahajuje řadič master prvkem startu, když fyzicky je vyvolána sestupná hrana signálu na vodiči SDA při současné HIGH hodnotě na vodiči sběrnice SCL. Vysílaný osmibitový znak je vysílán po vodiči SDA počínaje nejvýzamnějším bitem , úroveň na vodiči SDA musí zůstat stabilní po celou dobu trvání úrovně HIGH signálu sběrnicového vodiče SCL. Vyslaný znak je potvrzován přijímačem stažením signálu SDA na úroveň LOW v době, která odpovídá devátému bitu ( prvek ACK).

Přijímač může pozastavit vysílač podržením signálu SCL na úrovni LOW (prvek HOLD). To se týká každé periody signálu SCL a pozastavení může vyvolat libovolný prvek sběrnice.. Sestupná hrana signálu SCL navíc synchronizuje generátory signálu SCL připojených prvků.

Obr. 2: Časový průběh signálů SDA a SCL na sběrnici I2C

Popis rozhranní TWO WIRE mikrořadiče AVR

Základní vlastnosti obvodu TWO WIRE:

- Podpora můdu činnosti MASTER nebo SLAVE;

- Mikrořadič může být nakonfigurovaný jako vysílač nebo přijímač;

- Na sběrnici TWO WIRE lze pararelně připojit až 128 adresovaných podřízených (Slave) obvodů, využívá se sedmibitové adresování ( 27 = 128);

- Přenosová rychlost může být až 400 kHz;

- Výstupní budiče sběrnice mají omezenou rychlost změny hrany impulzu;

- Součástí obvodů rozhranní TWO WIRE jsou obvody pro potlačení šumu na obou linkách sběrnice;

- Rozhranní umožňuje plně nastavit adresu podřízeného obvodu včetně podpory současného přístupu ke všem obvodům na sběrnici;

- Rozhranní TWO WIRE umožňuje aktivaci mikrořadiče z úsporného režimu napájení (režim spánku).

Popis konfiguračních, stavových a datových I/O registrů rozhraní I2C mikrořadiče AVR Atmega32:

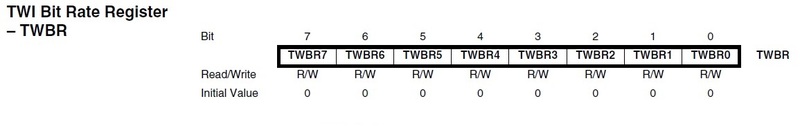

Tab. 1: Popis konfiguračních bitů I/O registru TWBR pro nastavení přenosové rychlosti sběrnice

Význam bitů registru TWBR:

Bity TWBR0 až TWBR7 nastavují přenosovou rychlost.

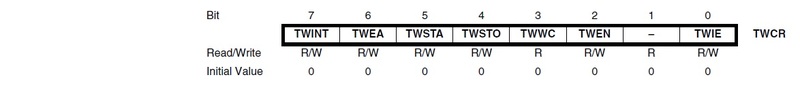

Tab. 2: Popis řídících bitů I/O registru TWCR

Význam bitů registru TWCR:

TWINT - příznak přerušení;

TWEA - ovolení potvrzování na TWI sběrnici;

TWSTA - start stav;

TWSTO - stop stav;

TWWC - příznak kolize zápisu;

TWEN - povolení činnosti TWI;

TWIE - povolení přerušení od TWI.

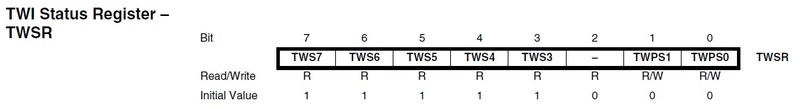

Tab. 3: Popis stavových bitů I/O registru TWSR

Význam bitů registru TWSR:

TWS3 až TWS7 - stavový kód TWI sběrnice;

TWPS0, TWPS1 - TWI předdělička.

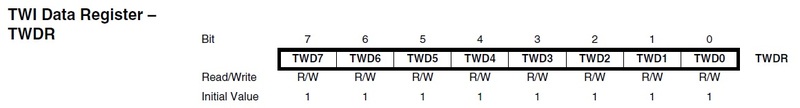

Tab. 4: Popis bitů datového registru TWI rozhranní

Význam bitů registru TWDR:

TWD0 až TWD7 - data pro obousměrný přenos.