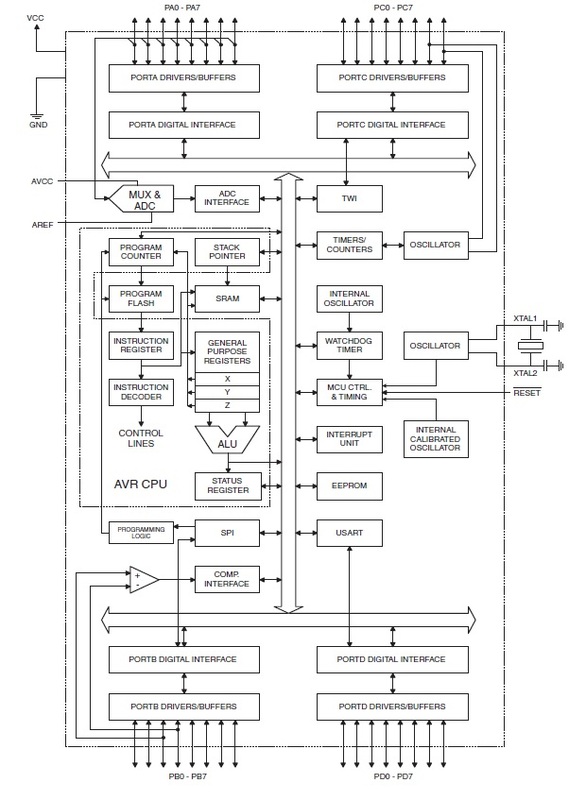

Popis architektury vnitřního obvodového zapojení mikrořadiče AVR

Architektura mikrořadiče AVR při pohledu na níže zobrazené funkční schéma se zdá být na první pohled složitá. Určitě architektura mikrořadičů AVR nepatří mezi ty nejjednodušší. Na druhou stranu po podrobnějším zkoumání a zorientování se ve funkčním schématu mikrořadiče AVR dojdeme k názoru, že složitost architektury je vykompenzována univerzálností, kterou nám mikrořadiče AVR poskytují. Z takovéhoto zjištění se následovně odvíjejí nejrůznější aplikace mikrořadičů AVR pro široké spektrum elektronických zařízeních.

Proto zkusíme se nejprve pohledem do funkčního schématu sestavit základní rysy konstrukce a z nich usoudit koordinaci činnosti jednotlivých vnitřních obvodů.

Obr. 1: Funkční schéma architektury mikrořadiče ATMEGA32

Předností architektury AVR mikrořadičů je koncepce rychle přístupného registrového pole. Toto pole obsahuje 32 tzv. pracovních registrů (general purpose registers) o osmi bitové velikosti. Přístup do registrového pole je vykonáván v jediném taktu strojového cyklu. Můžeme si to vyložit tak, že během jednoho hodinového cyklu lze vykonat jednu aritmeticko-logiclou operaci. Mikrořadiče AVR mají operační jádro typu RISC, mají redukovaný instrukční soubor a oddělenou paměť pro program a data.

Oba operandy aritmeticko-logické instrukce jsou načteny přímo z registrového pole během jednoho hodinového cyklu. Instrukce je provedena a výsledek je uložen opět do registrového pole. Ještě jednou je třeba vzít na vědomí, že tato operace je provedena v jedinném strojovém cyklu. Nepoužívají se zde žádné akumulační či vyrovnávací registry. Kdo ví o čem je řeč, musí být nadšený.

Data mezi jednotlivými obvody vnitřní strukury jsou mezi sebou přenášena pomocí osmibitové datové sběrnice. Tato sběrnice se táhne celým obvodem a je to taková informační dálnice, po které většina vnitřních obvodů komunikuje s okolím.

Vlastní program mikrořadiče je uložený v paměti flash (program flash), kde jednotlivé instrukce programu a jejich operandy jsou uloženy v 16-ti bitové šířce. Během činnosti mikrořadiče jsou jednotlivé instrukce vybírány z paměti programu k provedení pomocí čítače programu (program counter). Tento vlastně adresuje po každém inkrementování hodinovým impulzem příslušný řádek paměti programu tak, aby data instrukce a operandu mohla být rozkódována dekodérem instrukcí (instruction decoder). Dekodér instrukcí následovně vygeneruje větší množství impulzů na řídící sběrnici v takové časové posloupnosti, aby byla instrukce z paměti programu vykonána.

Pro nepřímé adresování jsou některé z pracovních registrů spojeny do registrových párů, které nesou označení X, Y, a Z. Pomocí těchto registrů můžeme zpětně přenastavit binární obsah čítače programu. Tato fukce se například používá pro větvení programu. Mimo přenastavení obsahu čítače programu se mohou 16-bitové registry X, Z, a Y použít pro nepřímé adresování datové paměti.

Paměť SRAM lze mimo metodu nepřímého adresování registry X, Y, a Z ještě adresovat obvodem ukazatele zásobníku paměti (stack pointer). Tento se skládá ze dvou osmibitových registrů SPL a SPH. Ukazatel zásobníku je schopen adresovat paměť SRAM na jejích nejvyšších adresách, kde je rezervované pole paměti pro zásobník. Zásobník je předurčen pro zálohování návratových adres při volání podprogramů, obsluh přerušení a nebo jenom pro prosté zálohování hodnot pracovních registrů.

Současné AVR lze charakterizovat:

- multifunkční, obousměrné vstupně/výstupní obecné porty s konfigurovatelnými, zabudovanými PULLUP rezistory;

- více vnitřních oscilátorů, včetně RC oscilátoru bez externích částí;

- vnitřní programovatelná Flash paměť až 256 KB (u verze Xmega až 384 KB);

- systémově programovatelné rozhranní ISP nebo odlaďovací JTAG;

- volitelnou Boot Code Section s nezávislým „zamykacím“ bitem pro ochranu;

- on-chip debugging pomocí JTAG rozhranní;

- vnitřní EEPROM paměť až 4KB;

- vnitřní SRAM paměť až 8 KB (u XMEGA až 32 KB);

- některé modely mají externí datový prostor o velikosti 64 KB (např. Mega8515, Mega162), tento prostor je překrytý interním datovým prostorem, proto se celých 64 KB neobjevuje na externí sběrnici;

- AVR obecně nepodporují spouštění kódu z externí paměti;

- 8bitové a 16ti-bitové časovače;

- PWM výstup (pro některé zařízení funguje jako generátor zpoždění);

- analogový napěťový komparátor;

- 10 ti-bitový A/D převodník s až 8 kanály;

- WDT (watchdog timer).

Mikrořadiče AVR obsahují různá sériová rozhraní, např.:

- TWI;

- UART/USART (používané např. s RS-232 nebo RS-485);

- SPI (Serial Peripheral Interface Bus).