Příklady zaměřené na minimalizaci logického výrazu

Příklad 1:

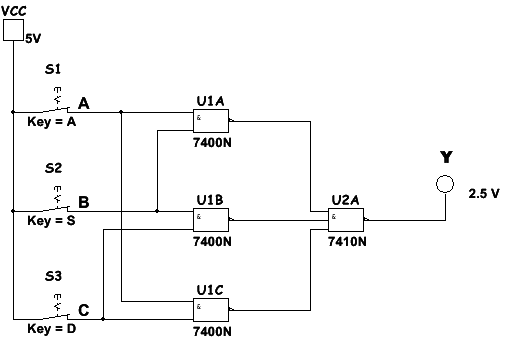

Navrhněte logický obvod pro tři proměnné, jehož výstupní proměnná nabývá logické hodnoty 1 jen tehdy, je-li většina vstupních proměnných ve stavu logické hodnoty 1:

Řešení:

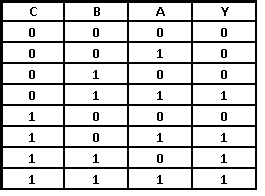

Obr. 1: Pravdivostní tabulka

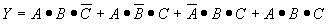

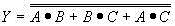

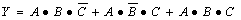

Výsledná logická funkce – úplný součtový tvar z pravdivostní tabulky:

Obr. 2: Realizace výsledné logické funkce bez minimalizace

Provedeme minimalizaci použitím pravidel Booleovy algebry, případně pomocí Karnaughovy mapy pro 3 proměnné.

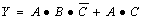

Výsledná logická funkce po minimalizaci:

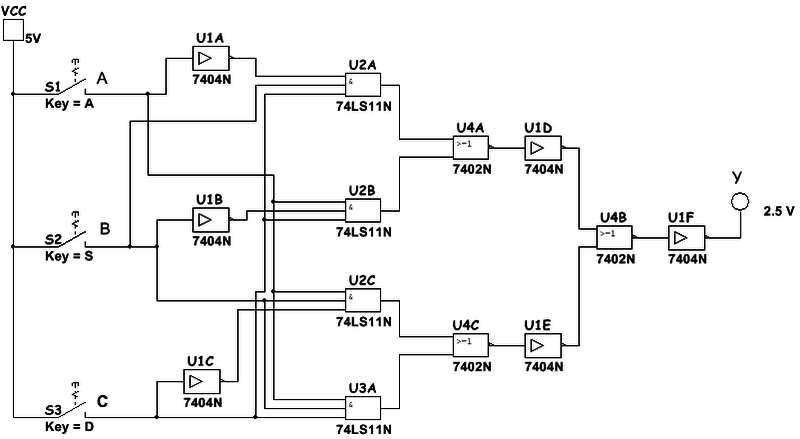

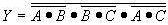

Realizace výsledné logické funkce pomocí hradel NAND:

Uvedenou funkci upravíme pomocí pravidla dvojí negace:

Úprava pomocí De Morganova zákona:

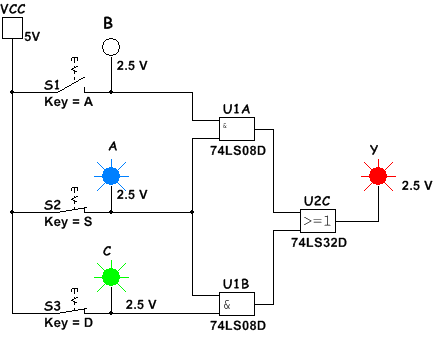

Obr. 3: Schéma zapojení zminimalizované funkce

1. Činnost logické funkce Y ověřte pomocí výukového systému rc2000

a) Modulem LOG SELECTOR zadávejte vstupní kombinace a modulem LOG PROBE sledujte výstupní hodnoty.

b) Připojením k PC INTERFACE v módu digitální vstup/výstup zkontrolujte správnost obvodu.

2. Správnost zapojení a činnost logické funkce Y proveďte pomocí SW Multisim 11.

3. Ověřte činnost dané logické funkce na nepájivém poli.

4. Zakreslete do sešitu pravdivostní tabulku měřené logické funkce a porovnejte je se zadanými.

Příklad 2:

Vyjádřete logickou funkci v pravdivostní tabulce algebraickým zápisem v součtovém tvaru. Pomocí pravidel Booleovy algebry nebo pomocí Karnaughovy mapy součtový tvar logické funkce zjednodušte, nakreslete a ověřte výsledné zapojení při použití logických hradel NAND:

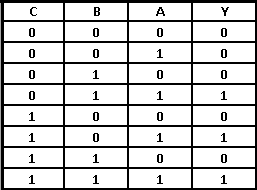

Obr. 4: Pravdivostní tabulka

Řešení:

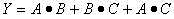

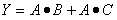

Z pravdivostní tabulky napíšeme logický výraz pro výslednou funkci v součtovém tvaru

Použijeme pravidlo vyloučení třetího

Výraz zjednodušíme použitím pravidla absorpce negace

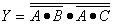

Výsledný výraz upravíme pomocí DeMorganova pravidla pro realizaci pomocí logických členů NAND

Obr. 5: Realizace výsledné logické funkce pomocí SW Multisim

1. Činnost logické funkce Y ověřte pomocí výukového systému rc2000

a) Modulem LOG SELECTOR zadávejte vstupní kombinace a modulem LOG PROBE sledujte výstupní hodnoty.

b) Připojením k PC INTERFACE v módu digitální vstup/výstup zkontrolujte správnost obvodu.

2. Správnost zapojení a činnost logické funkce Y proveďte pomocí SW Multisim 11.

3. Ověřte činnost dané logické funkce na nepájivém poli.

4. Zakreslete do sešitu pravdivostní tabulku měřené logické funkce a porovnejte je se zadanými.

- CZ.1.07/1.5.00/34.0093 Inovace výuky na VOŠ a SPŠ Šumperk

Obrázky

-

Archiv autora

Jak znějí a k čemu se používají De Morganovy zákony?