Klopný obvod typu J-K

Klopný obvod J-K vznikne ze synchronního klopného obvodu RS, když zpětně přivedeme logické stavy z výstupů Q a NonQ na vstupní obvody AND.

Realizujte synchronní R-S klopný obvod J-K s hradly NAND a AND a ověřte jeho činnost:

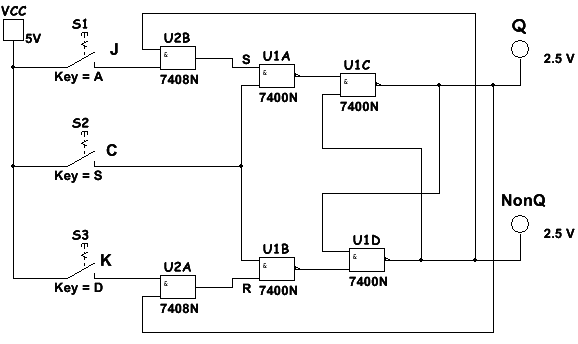

Obr. 1: Schéma zapojení synchronního J-K obvodu

1. Činnost klopného obvodu ověřte pomocí výukového systému rc2000:

a) Modulem LOG SELECTOR zadávejte vstupní kombinace a modulem LOG PROBE sledujte výstupní hodnoty.

b) Připojením k PC INTERFACE v módu digitální vstup/výstup zkontrolujte správnost obvodu.

2. Správnost zapojení a činnost klopného obvodu proveďte pomocí SW Multisim 11.

3. Ověřte činnost klopného obvodu na nepájivém poli.

4. Zakreslete do sešitu časový diagram klopného obvodu.

Synchronní klopný obvod typu J-K (Master – Slave)

Tento typ klopného obvodu je nejpoužívanější. Toto řešení je zvoleno proto, aby zpětné vazby nebyly účinné během synchronizačního impulsu (mohlo by dojít k nekontrolovatelnému kmitání). Výstupem tohoto zapojení je výstup z "podřízeného" klopného obvodu (Slave). Vstupy tohoto podřízeného klopného obvodu jsou řízeny výstupy z hlavního klopného obvodu (Master). Vstupy J a K tohoto zapojení určují stav hlavního klopného obvodu. Hodinový signál je přiváděn do obou částí zapojení, pro podřízený obvod je však invertován. Při C=1 se informace zapamatovává prvním klopným obvodem (Master). Podřízený klopný obvod ovšem po tuto dobu nebude reagovat na výstupy hlavního obvodu, protože na jeho vstup hodin se přivádí signál invertovaný. Zůstane-li na nějakou chvíli hodinový signál na úrovni H, ustálí se stav hlavního obvodu, zatímco podřízený obvod bude nadále blokován a nebude reagovat na stav výstupů hlavního obvodu. Při přechodu hodinového signálu C z 1 do 0 se první klopný obvod oddělí od vstupu a přestane reagovat na stav svých J, K vstupů. Invertovaný hodinový signál na vstupu podřízeného klopného obvodu způsobí, že zareaguje na stav výstupů Q a NonQ hlavního klopného obvodu. Informace se objeví na výstupu J-K klopného obvodu a krátce po sestupné hraně vstupního hodinového impulsu se stav výstupů podřízeného obvodu ustálí. Hlavní klopný obvod nebude reagovat na změny svých vstupů J a K, dokud nepřijde nový pozitivní hodinový impuls.

J-K klopné obvody se vyrábějí jako obvody typu TTL

Technické údaje logické členu najdete na adrese:

http://www.ti.com/lit/ds/symlink/sn74f112.pdf

Realizujte dvoufázový synchronní R-S klopný obvod J-K s hradly NAND a ověřte jeho činnost:

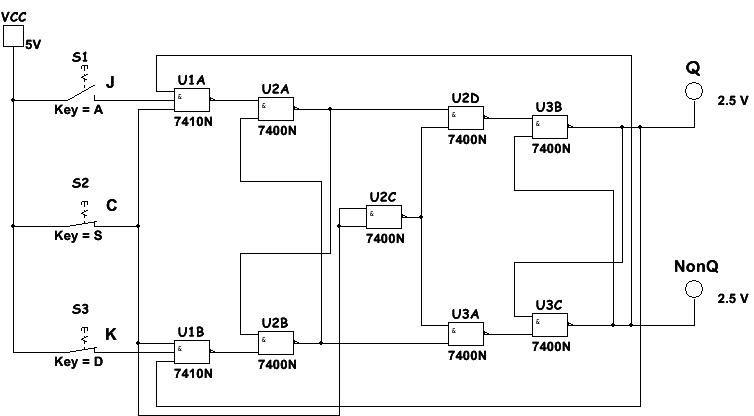

Obr. 2: Schéma zapojení dvojfázového synchronního J-K obvodu

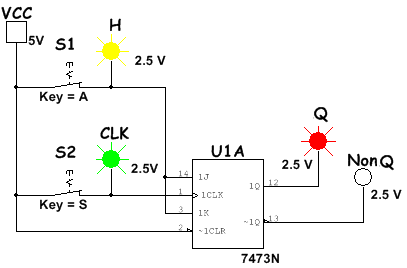

Obr. 3: Schéma zapojení synchronního J-K obvodu 7473

1. Činnost klopného obvodu ověřte pomocí výukového systému rc2000:

a) Modulem LOG SELECTOR zadávejte vstupní kombinace a modulem LOG PROBE sledujte výstupní hodnoty.

b) Připojením k PC INTERFACE v módu digitální vstup/výstup zkontrolujte správnost obvodu.

2. Správnost zapojení a činnost klopného obvodu proveďte pomocí SW Multisim 11.

3. Ověřte činnost klopného obvodu na nepájivém poli.

4. Zakreslete do sešitu časový diagram klopného obvodu.

Schéma zapojení:

- CZ.1.07/1.5.00/34.0093 Inovace výuky na VOŠ a SPŠ Šumperk

Obrázky

- Archiv autora

- Popište funkci klopného obvodu J-K.

- Popište funkci dvoustupňového J-K klopného obvodu.

- Jak pracuje jednofázový klopný obvod J-K při trvalém stavu J=K=1?

- Jak pracuje dvoufázový klopný obvod J-K při trvalém stavu J=K=1?

- Dvojčinné klopné obvody (Master-Slave) sestávají ze dvou stupňů klopných obvodů. První klopný obvod ukládá při Clk=1 vstupní stavy do mezipaměti a při sestupné hraně hodinového signálu je přenáší do druhého klopného obvodu.

- Připojíme-li vstupy J a K klopného obvodu J-K na logickou 1, mění se při každém úplném impulsu na hodinovém vstupu výstupní stav. Na výstupu klopného obvodu vzniká sled impulsů s polovičním počtem impulsů než byl počet vstupních impulsů. Klopný obvod je dělič 2:1.