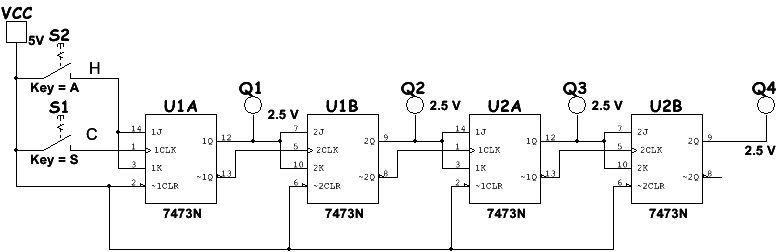

Asynchronní čítač s KO typu J-K

Realizujte čítač vpřed s klopnými obvody typu J-K a ověřte jeho činnost:

Obr. 1: Schéma zapojení asynchronního čítače vpřed s KO typu J-K

1. Činnost čítače ověřte pomocí výukového systému rc2000:

a) Modulem LOG SELECTOR zadávejte vstupní kombinace a modulem LOG PROBE sledujte výstupní hodnoty.

b) Připojením k PC INTERFACE v módu digitální vstup/výstup zkontrolujte správnost obvodu.

2. Správnost zapojení a činnost čítače proveďte pomocí SW Multisim 11.

3. Ověřte činnost čítače na nepájivém poli.

4. Zakreslete do sešitu časový diagram čítače.

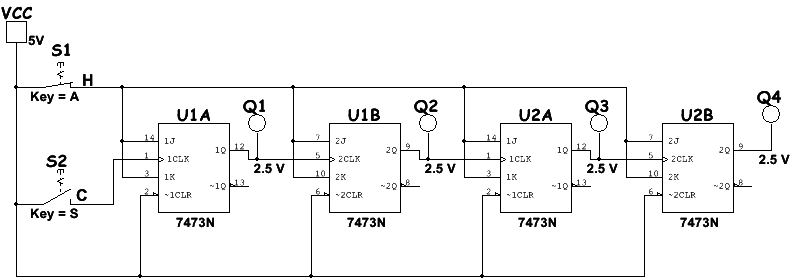

Realizujte čítač vzad s klopnými obvody typu J-K a ověřte jeho činnost:

1. Činnost čítače ověřte pomocí výukového systému rc2000:

a) Modulem LOG SELECTOR zadávejte vstupní kombinace a modulem LOG PROBE sledujte výstupní hodnoty.

b) Připojením k PC INTERFACE v módu digitální vstup/výstup zkontrolujte správnost obvodu.

2. Správnost zapojení a činnost čítače proveďte pomocí SW Multisim 11.

3. Ověřte činnost čítače na nepájivém poli.

4. Zakreslete do sešitu časový diagram čítače.

Obr. 2: Schéma zapojení asynchronního čítače vzad s KO typu J-K

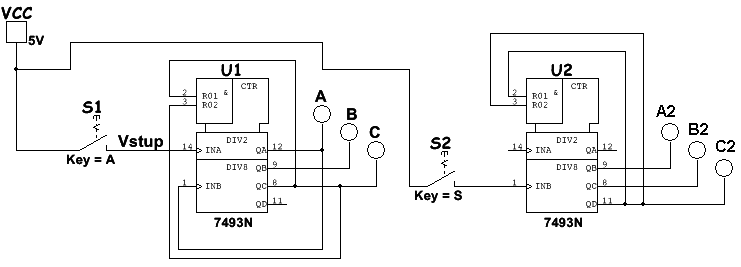

Realizujte čtyřbitový binární čítač modulo 4 a ověřte jeho činnost:

Pojem “modulo 4” znamená, že po příchodu čtvrtého čítaného impulsu se čítač automaticky vynuluje, tj. na výstupu všech klopných obvodů se nastaví 0 a při dalším čítaném impulsu počítá čítač znovu od 1. Stav čítače nechť je reprezentován signály na dostupných výstupech jednotlivých užitých klopných obvodů. Čítač má mít možnost zpětného nastavení (nulování) vnějším signálem.

1. Činnost čítače ověřte pomocí výukového systému rc2000:

a) Modulem LOG SELECTOR zadávejte vstupní kombinace a modulem LOG PROBE sledujte výstupní hodnoty.

b) Připojením k PC INTERFACE v módu digitální vstup/výstup zkontrolujte správnost obvodu.

2. Správnost zapojení a činnost čítače proveďte pomocí SW Multisim 1.

3. Ověřte činnost čítače na nepájivém poli.

4. Zakreslete do sešitu časový diagram čítače.

Obr. 3: Schéma zapojení čtyřbitového binárního čítače 7493

Technické údaje logické členu najdete na adrese:

- CZ.1.07/1.5.00/34.0093 Inovace výuky na VOŠ a SPŠ Šumperk

Obrázky

- Archiv autora