Princip činnosti základních typů JFET tranzistorů

JFET je tranzistor řízený elektrickým polem, u kterého je nahrazen izolant mezi řídicí elektrodou a kanálem tranzistoru a přechodem PN působícím v závěrném směru, jak je to znázorněno na obrázku 1.

Obr. 1: Princip tranzistoru JFET

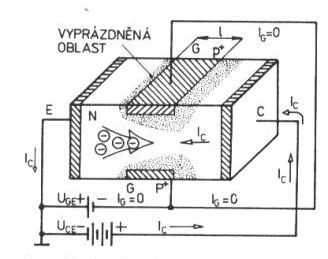

Základem JFET je polovodičová destička s nevlastní vodivostí typu N, případně P (viz obr. 2). Destička je opatřená na obou koncích kovovými kontakty, které slouží jako kontaktní plochy pro vývod. Do dolní a horní stěny základní destičky jsou difúzí vytvořeny silně dotované oblasti opačného typu vodivosti, než jakého je typ vodivosti základní destičky. To znamená, má-li základní destička vodivost typu N, budou v ní vytvořeny oblasti typu P+, v destičce typu P budou vytvořeny oblasti typu N+, které tvoří hradla (GATE).

Obr. 2: Principy, uspořádání a schematické značky JFET

Třívývodový tranzistor má obě hradla propojena, čtyřvývodový tranzistor má hradla vyvedena samostatně.

Základem správné činnosti tohoto typu tranzistoru je nahrazení izolační vrstvy závěrně polarizovaným PN přechodem.

Jak je známo z popisu diod, je na polovodičovém závěrně polarizovaném přechodu PN silné elektrické pole, které zabraňuje, aby do něho pronikaly většinové (majoritní) nosiče proudu.

POZNÁMKA: Další popis je prováděn pro JFET s kanálem typu N.

Ochuzená (vyprázdněná) oblast

Při polarizaci přechodu PN mezi hradlem a emitorem v závěrném směru (to znamená, že na vývodu P je záporné napětí a na vývod N kladné), proud přechodem téměř neprochází a v okolí přechodu se rozšíří vrstva, která neobsahuje volné nosiče náboje. Se zvětšováním závěrného napětí se tato oblast rozšiřuje.

Protože neobsahuje volné většinové nosiče náboje, nazývá se tato oblast „ochuzená“. Můžeme se na ni dívat jako na dielektrikum a permitivitou příslušného polovodiče.

Velikost ochuzené oblasti je závislá na :

-

velikosti napětí mezi hradlem a emitorem UGS;

-

a na velikosti napětí mezi kolektorem a emitorem UDS.

Šířka kanálu

Vyprázdněná oblast přidružená k hradlům G určuje šířku kanálu tranzistoru. Šířce kanálu je úměrná velikost proudu kolektoru ID. Kanál je tvořen prostorem mezi vyprázdněnými oblastmi, jak je znázorněno na obrázku 1.

Čím je kanál širší, tím je jeho odpor menší a může jím protékat větší proud. Z uvedeného hlediska můžeme tranzistor JFET při konstantní velikosti napětí UDS mezi kolektorem a emitorem považovat za proměnný odpor řízený napětím UGS mezi hradlem a emitorem.

Při proměnné velikosti UDS mezi kolektorem a emitorem je JFET v podstatě napětím řízený zdroj proudu, velikost kolektorového proudu ID je úměrná velikosti napětí UGS mezi hradlem G a emitorem E 〔iD = f(uGS)〕.

Šířka kanálu závisí na kombinaci velikostí napětí UDS a UGS.

Kanál má podle typu tranzistoru vodivost typu N nebo vodivost typu P a neobsahuje žádný přechod PN, a proto je proud mezi kolektorem a emitorem zprostředkováván pouze většinovými (majoritními) nosiči náboje. Protože je vedení proudu v kanálu způsobeno pouze nosiči náboje jedné polarity, patří i tyto tranzistory mezi unipolární, přestože tranzistor sám PN přechody obsahuje (ty sice kanál řídí, ale na vedení proudu v něm se nepodílí).

POZNÁMKA: Protože je při činnosti tranzistoru PN přechod hradlo-kanál polarizován v závěrném směru, protéká hradlem pouze zanedbatelný proud rovný závěrnému proudu polovodičové diody. Elektrické pole je v tranzistoru vytvořeno napětím připojeným na hradlo, a proto je řídícím parametrem tranzistorů FET velikost napětí UGS na řídicí elektrodě.

Důležitá ZÁSADA! Polarity napětí UGS mezi hradlem a emitorem a napětí UDS mezi kolektorem a emitorem musejí být takové, aby byl při všech přípustných hodnotách napětí UDS přechod PN mezi hradlem a kanálem za všech okolností polarizován v závěrném směru.

Při nedodržení této zásady může dojít ke zničení tranzistoru!

Činnost JFET (viz obr. 1)

Činnost JFET je založena na řízení velikosti efektivního průřezu polovodičového kanálu pomocí přechodu PN.

Při zvětšování závěrného napětí mezi hradlem a emitorem se zvětšuje šířka ochuzené (vyprázdněné) vrstvy přechodu a tím se zmenšuje šířka kanálu.

Nechť UGS = 0 (proud kolektoru ID = 0, podél kanálu nevzniká žádný úbytek napětí) a zároveň nechť vzrůstá napětí UDS. Zpočátku, při malém napětí UDS, jsou tloušťky ochuzené vrstvy obou přechodů po celé délce kanálu stejné. S rostoucím napětím UDS dochází ke zvětšování závěrného napětí na přechodu PN mezi hradlem G a kolektorem D. To způsobí rozšíření ochuzené vrstvy převážně blíže ke kolektoru D. To také způsobí zvětšení velikosti efektivního odporu kanálu a zmenšení vlivu velikosti UDS na velikost proudu kolektoru ID.

Rozšiřování ochuzené vrstvy vlivem vzrůstu kolektorového napětí UDS pokračuje až do okamžiku, kdy se obě ochuzené oblasti spojí. Přitom UDS = UP, kde Up je tzv. napětí zaškrcení kanálu.

Zaškrcená oblast je tvořena vyprázdněnými oblastmi vykazujícími velký odpor. Přesto i nyní protéká kanálem proud ID, protože potenciál UDS působí podél kanálu a ne napříč, jak tomu je při vysoké hodnotě napětí UGS mezi hradlem a emitorem. Vyprázdněná oblast pro elektrony představuje oblast velkého odporu, kterou překonávají díky působení silného elektrického pole vyvolaného napětím UDS.

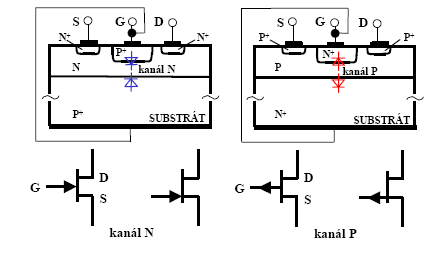

Výstupní charakteristika

Popsaný děj můžeme znázornit pomocí výstupní charakteristiky pro určitou zvolenou hodnotu UGS (obr. 3). Zvětšujeme-li napětí UDS mezi kolektorem a emitorem, vzrůstá zpočátku proud kanálem ID a zároveň se zvětšuje úbytek napětí na ohmickém odporu kanálu.

Obr. 3: JFET - výstupní charakteristika

Výstupní charakteristika tranzistoru má dvě oblasti, ve kterých se tranzistor chová různě:

-

triodovou (odporovou);

-

oblast saturace (nasycení).

V triodové oblasti je proud kolektoru ID úměrný napětí na kolektoru a tranzistor se chová jako rezistor.

Při určité hodnotě napětí kolektoru UDS = UP = UDSsat dojde k tomu, že se kolektorový proud zvětšovat přestane. V oblasti saturace (nasycení) protéká kolektorem téměř konstantní proud. Napětí mezi kolektorem a emitorem UDS má na velikost protékajícího proudu jen velmi malý vliv. V této oblasti je velikost proudu ID závislá pouze na velikosti napětí UGS na hradle tranzistoru.

POZNÁMKA: Oblast saturace nemá nic společného se saturačním napětím a oblastí saturace bipolárních tranzistorů.

Čtyřpólové charakteristiky tranzistorů JFET

Stejně jako bipolární tranzistory i tranzistory JEFT jsou používány ve čtyřpólovém zapojení. Proto jsou u nich používány čtyřpólové charakteristiky.

Na obrázku 3 jsou charakteristiky rozděleny na dvě oblasti - na oblast odporovou a oblast saturace. V odporové oblasti se proud kanálem tranzistoru se zvětšujícím se napětím mezi kolektorem a emitorem UDS lineárně zvětšuje.

V oblasti saturace je proud kolektoru ID protékající mezi emitorem a kolektorem tranzistoru JEFT řízen změnou napětí UGS na řídicí elektrodě G (velikostí napětí UGS je řízena šířka kanálu, tím velikost jeho odporu a v závislosti na tom velikost kolektorového proudu ID).

V případě tranzistoru s kanálem typu N musí být napětí UGS záporné. Může se pohybovat od nuly do několika voltů.

POZNÁMKA: Výše uvedený popis byl uskutečněn pro tranzistory s kanálem typu N. Rozdíl mezi tranzistorem a kanálem N a tranzistorem s kanálem P spočívá v tom, že tranzistor s kanálem P má hradla tvořena polovodičem typu N+ a kanál je polovodičem typu P. JFET s kanálem P má opačnou polaritu připojených napětí oproti popsanému JFET s kanálem typu N. V praxi je tranzistor typu N označován jako N JFET, s kanálem typu P jako P JFET.

Důležité parametry tranzistorů JFET

Provozní parametry

-

IDSS je maximální (saturační) proud kolektoru D do emitoru S při nulovém napětí mezi hradlem a emitorem (UGS = 0). Jeho velikost závisí na napětí UDS, a proto je udáván pro určité napětí mezi kolektorem a emitorem ( IDSS = min 1 mA, IDSS = max 5mA, UDS = 15 V, UGS = 0);

-

UGS(off) je napětí zaškrcení kanálu pro definované podmínky:

-

Šířka kanálu závisí na kombinaci napětí UGS a UDS. Při určité velikosti UGS dojde k částečnému (místnímu) zaškrcení kanálu. Od těchto hodnot napětí UGS a UDS se kolektorový proud tranzistoru téměř nezvyšuje. Jestliže UGS = UGS (off), dojde k zaškrcení po celé délce kanálu. Hodnota je udána pro určitou velikost UDS a ID, a například UDS = 15 V, ID = 0,5 nA.

-

Při dosažení UGS(off) zaplní vyprázdněné oblasti PN přechodů celý průřez pod hradlem a zabrání průchodu elektrických nábojů. Odpor rDS(off) kanálu přitom nabude velmi vysoké hodnoty.

-

-

rDS(off) je odpor mezi kolektorem a emitorem tranzistoru při zavřeném kanálu;

-

rDS(on) je odpor otevřeného kanálu;

-

Up je napětí zaškrcení kanálu pro danou velikost napětí UGS;

-

UDS sat je napětí mezi kolektorem a emitorem, kdy dojde k zaškrcení kanálu vlivem napětí UDS, když UGS = konst. Se zvětšováním UDS od nuly se zvětšuje proud kanálem ID, tím roste i úbytek napětí na odporu kanálu, napětí není rovnoměrně v kanálu rozloženo, ale je největší u kolektoru a nejmenší u emitoru. Vlivem tohoto napětí se zvětšuje šířka ochuzené vrstvy, vodivý kanál se směrem ke kolektoru zužuje. Proud kolektoru se již lineárně nezvětšuj, až dojde k situaci, kdy se v blízkosti kolektoru ochuzené vrstvy propojí a nastává místní zaškrcení kanálu. Kolektorový proud se nyní již nezvyšuje.

Mezní parametry tranzistorů JFET

-

UBRDS je průrazné napětí mezi kolektorem a emitorem, při jehož překročení může dojít ke zničení tranzistoru;

-

PDmax je maximálnjí ztrátový výkon tranzistoru (PD= UDS . ID);

-

UBRGSS je průrazné napětí přechodu mezi hradlem G a emitorem S, které je definováno pro UDS = 0, IG = 1μA (např. -25 V, - 40 V,….);

-

UGSmax (též IGSS) Protože se může stát, že přechod hradlo G – emitor S, bude polarizován v propustném směru, je stanoveno omezení proudu tohoto přechodu v propustném směru (je to parametr ekvivalentní meznímu proudu v propustném směru polovodičové diody, např. 100 nA.)

Využití tranzistorů JFET

Stejně jako bipolární tranzistory je možné použít i tranzistory JFET v aplikacích zpracování lineárních signálů nebo v dvoustavových aplikacích (spínání různých typu zátěží, přenos dvoustavové informace). Ve spínacím režimu je v závislosti na vstupním signálu kanál buď otevřený (má malý odpor), nebo zavřený.

V oblasti malých napětí UDS se tranzistor chová jako lineární odpor, jehož velikost je možné řídit velikostí napětí UGS.

Unipolární tranzistor jako spínací prvek

Použití tranzistorů řízených polem ve funkci spínacího prvku má řadu výhod:

-

izolované hradlo umožňuje téměř dokonalé oddělení řídicího a spínaného obvodu;

-

tranzistory řízené polem umožňují spínat signály mající kladnou i zápornou polaritu napětí;

-

protože neobsahují přechod PN jako bipolární tranzistory, neprojevuje se u nich nutnost zotavení přechodu PN při otevírání nebo zavírání tranzistoru;

-

protože mezi kolektorem a emitorem není žádný přechod PN, neprojevuje se napěťový posuv způsobený napětím na tomto přechodu jako u bipolárních tranzistorů;

-

protože má FET při sepnutí odpor rDS(on) řádově jednotky až stovky ohmů a v rozepnutém stavu řádově MΩ, je vhodný pro použití ve funkci spínače (poměr odporů v sepnutém a rozepnutém stavu je velký).

Nevýhoda použití tranzistorů řízených polem ve funkci spínacího prvku:

-

při vyšších kmitočtech se projevuje vliv vnitřních kapacit, což má za následek pokles impedance uzavřeného FETu;

-

rychlost spínání je omezena vnitřními kapacitami tranzistoru.

JFET jako napětím řízený odpor

Možnost této aplikace vyplývá z toho, že kolektorový odpor mezi kolektorem a emitorem je možné v odporové oblasti lineárně měřit řídicím napětím na hradle tranzistoru.

Při uvedeném použití je tranzistor provozován v lineární odporové oblasti s napětím mezi kolektorem a emitorem menším než asi 100 až 200 mV.

Přibližně do uvedených hodnot napětí mezi kolektorem a emitorem jsou výstupní charakteristiky tranzistoru JFET lineární a souměrné kolem počátku souřadnic. Kolektorový proud je lineárně závislý na kolektorovém napětí, napětí na kolektoru může být kladné nebo záporné.

Voltampérové charakteristiky jsou charakteristikami odporů. Lineární závislost proudu na přiloženém napětí charakterizuje lineární rezistor.

Parametrem výstupních charakteristik je napětí UGS, takže změnou tohoto napětí je možné měnit hodnotu odporu. Se zvětšováním záporné hodnoty napětí UGS (pro NJFET) dochází ke zmenšování šířky kanálu a zároveň i velikosti jeho odporu.

Model tranzistorů řízených elektrickým polem pomocí čtyřpólových parametrů

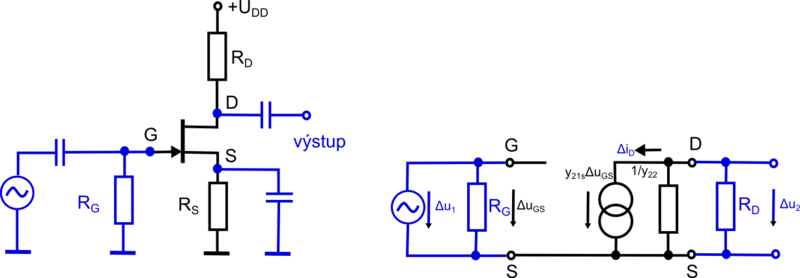

Při návrhu zesilovače malých signálů s tranzistory řízenými elektrickým polem je výhodné používat admitanční parametry (náhrada vstupu i výstupu tranzistoru podle Nortonova teorému).

Zjednodušený model unipolárního tranzistoru pro zapojení se společným emitorem v oblasti nízkých kmitočtů pomocí admitančních parametrů je znázorněn na obr. 4.

Protože je vstupní impedance tranzistorů FET na nízkých kmitočtech velmi vysoká, je y11e≅0, je možné tento parametr ve schématu nahradit rozpojeným obvodem.

Ve schématu je zanedbán také parametr y12 vyjadřující zpětný vliv výstupního napětí na vstup tranzistoru.

Výstupní část náhradního schématu je nahrazena výstupní admitancí a ekvivalentním zdrojem proudu řízeným velikostí signálového napětí y21e . ΔuGS.

Parametry y21e určuje strmost převodní charakteristiky, má rozměr vodivosti a má název strmost. Určuje, kolikrát se se změnou vstupního napětí ΔuGS změní výstupní proud iD.

Tranzistory řízené elektrickým polem jsou prvky řízené napětím.

Obr. 4: JFET jako zesilovač, admitanční model tranzistoru JFET