Unipolární tranzistory ve spínacím režimu

Dosud popisované tranzistory MOSFET a JFET bývají vzhledem k horizontální poloze kanálu nazývány horizontální FET. Jejich kanál je vzhledem ke konstrukci poměrně tenký, a proto má při otevřeném kanálu v porovnání s bipolárním tranzistorem větší odpor. Kvůli nutnosti odvodu tepla (teplo se vyvíjí v kanálu, tedy v blízkosti povrchu) a relativně velkému odporu otevřeného kanálu nejsou vhodné pro použití nad kolektorové ztráty o velikosti přibližně PD ≅ 100 mW.

Pro větší proudy byly vyvinuty vertikální struktury výkonových tranzistorů FET, ve kterých je kanál vytvořen kolmo na povrch polovodiče. Vertikální uspořádání je označováno písmenem V, tedy VMOSFET.

Tranzistory jsou vyráběny ve dvou provedeních označovaných jako Logic-level FET a Standard-level FET.

Tranzistory označené jako Logic-level FET jsou kompatibilní s úrovněmi logických obvodů. Prahové napětí u této kategorie tranzistorů je zpravidla 2 až 4 V. Nižší prahové napětí než 2 V není vhodné, protože, jak je známo, zmenšuje se jeho velikost s teplotou a při vyšší teplotě by mohlo docházet k pootevření tranzistoru při přiblížení prahového napětí a povolené úrovně log 0 logických obvodů.

Hlavní principy uspořádání výkonových tranzistorů FET

-

výkonové tranzistory JFET;

-

struktury SIT;

-

nízkonapěťová struktura se žlábkem tvaru V, název VMOS (VVMOS);

-

vysokonapěťová planární struktura s dvojí difúzí, název DMOS (VDMOS).

Výkonové tranzistory JFET

Stejně jako nízkovýkonové i výkonové tranzistory JFET jsou součástky s hradlem izolovaným závěrně polarizovaným přechodem PN. Napětí záporně polarizovaného hradla vytváří pod hradlem ochuzenou oblast, která zužuje kanál mezi emitorem S a kolektorem D, a tím zmenšuje jeho vodivost.

Struktura výkonového tranzistoru JFET je znázorněna na obrázku 1.

Jak je z obrázku zřejmé, proud protéká od kolektoru směrem k emitoru vertikálně.

Obr. 1: Struktura výkonového JFET v provedení SIT a) technická realizace b) základní uspořádání

Výkonové tranzistory SIT

Tranzistory SIT (Static Induction Transistor) – jedná se v podstatě o tranzistory JFET. Konstrukce je založena na paralelním propojení struktur s velmi krátkým kanálem. Hradla, vnořená dovnitř kanálu tranzistoru mezi emitor a kolektor, působí podobně jako mřížka v elektronce triodě. Přivedením závěrného napětí na hradlo se v okolí vnořených částí hradla vytvářejí oschuzené oblasti, které zužují vodivé oblasti kanálu, a tak zužují celkovou šířku kanálu a zmenšují velikost proudu protékajícího mezi kolektorem D a emitorem S.

Protože je technologie těchto tranzistorů velmi náročná, je cena značně vysoká. Proto jsou tranzistory SIT používány zřídka

Výkonové tranzistory SIT pro oblast UHF

Tyto tranzistory jsou vertikální tranzistory MESFET s krátkým kanálem. Jejich největší výhodou je vysoká výkonová hustota (velký výkon na plochu – přibližně 300 kW/cm2) a vysoký mezní kmitočet dosahující velikosti fT = 7 GHz.

Vhodným materiálem pro výrobu těchto tranzistorů je karbid křemíku SiC, je používán také nitrid galitý GaN, který poskytuje velkou pohyblivost elektrických nábojů a vysokou teplotní vodivost.

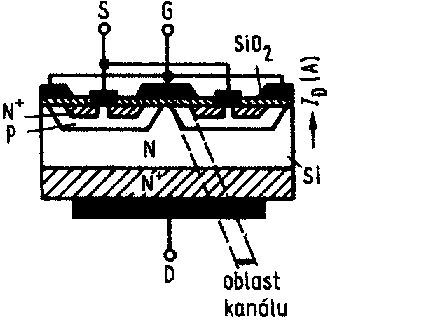

Výkonové tranzistory MOSFET

Hlavní typy výkonových unipolárních tranzistorů využívaných ve výkonových obvodech jsou tranzistory založené na řízení šířky kanálu izolovaným hradlem IGFET. Nejčastěji používanými strukturami jsou struktury VMOSFET a DMOSFET.

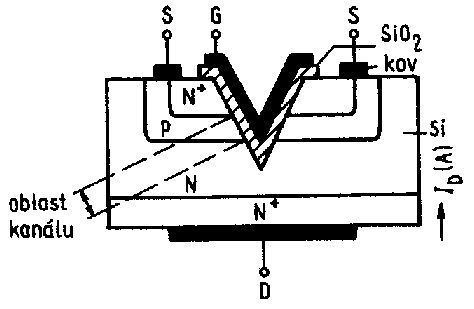

Výkonové tranzistory VMOS (UMOS)

Dalším typem výkonových tranzistorů jsou tranzistory VVMOS (dále jen VMOS)

Obr. 2: Struktura tranzistoru VMOS

Jak je vidět z obrázku 2, tranzistor struktury VMOS má ve své struktuře žlábek ve tvaru V – z toho byl odvozen jeho název /struktura byla používána v 80. letech pro menší proudy. Dnes v katalozích nalezneme hlavně modifikované struktury UMOS, jsou to modifikované zdokonalené verze tranzistorů VMOS, u kterých nemá hradlo tvar ostrého V, ale špička je nahrazena vodorovným úsekem).

Nevýhodou struktury VMOS (UMOS) je omezení maximálního napětí UUDSM. Proto je tranzistor se strukturou VMOS vyráběn převážně pro menší napětí. Pro větší napětí jsou využívány tranzistory se strukturou DMOS s kanálem typu N (nebo dvojice N a P).

Obr. 3: DMOS v provedení SIPMOSFET firmy SIEMENS

Obr. 4: Pouzdro tranzistoru DMOS firmy RF