Organizace pracovních registrů mikrořadičů a paměti RAM mikrořadičů AVR

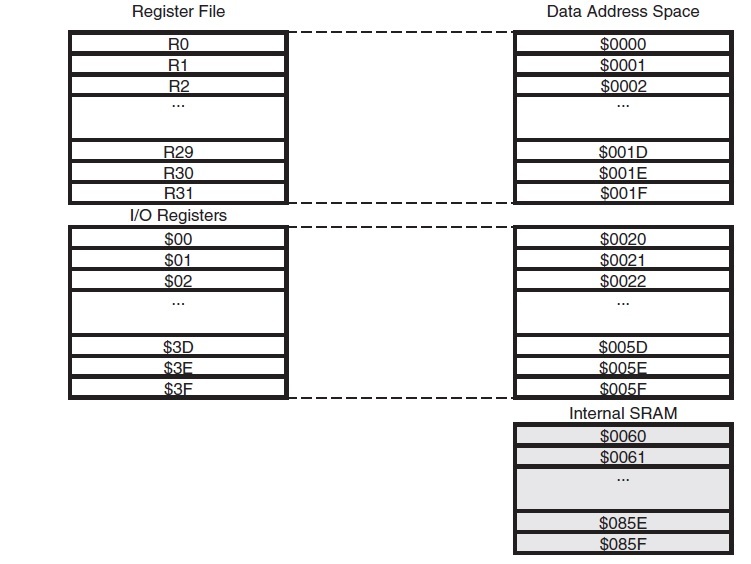

Obr. 1: Organizace paměti RAM mikrořadiče AVR

Registrové pole (Register file) mikrořadičů AVR

Je tvořeno skupinou 32 registrů o délce 8-bitů. Umístění těchto registrů je v paměti SRAM mikrořadiče na jejím začátku adresovaného prostoru. Obsazení adres odpovídá hodnotám od 0x00 do 0x1F. Tyto registry jsou číselně rozlišeny, když regostr R0 je umístěný na adrese 0x00 a nejvyšší registr R31 je umístěný na adrese 0x1F. Registrové pole pracovních registrů má přímý přístup k aritmeticko-logické jednotce mikrořadiče. Toto uspořádání značně zjednodušuje algoritmizaci programu, což v konečném důsledku vede k rychlejšímu zpracování instrukcí mikrořadičem.

Vstupně/výstupní registry (I/O Memory)

Jedná se o pole speciálních funkčních registrů, které ovládají vestavěné periferie a řídí činnost mikrořadiče. Pro tyto registry je vymezený prostor o velikosti 64 adres, a to v rozsahu od 0x20 do 0x5F.

Tab. 1: I/O pracovních registrů

| Registr | Dtručný popis funkce |

| SREG | Stavový registr |

| SPL | Ukazatel zásobníku dolní byte |

| SPH | Ukazatel zásobníku horní byte |

| TIMSK | Maskování přerušení čítačů/časovačů |

| TIFR | Příznaky přerušení čítačů/časovačů |

| MCUCR | Řídící registr mikrořadiče |

| MCUCSR | Obecný řídící/ stavový registr mokrořadiče |

| TCCR0 | Řídící registr čítače/časovače 0 |

| TCNT0 | Obsah čítače/časovače 0 |

| OCR0 | Komparační registr čítače/časovače 0 |

| ASSR | Stavový registr asynchronního režimu (čítače/časovače 2) |

| TCCR1A | Řídící registr A čítače/časovače 1 |

| TCCR1B | Řídící registr B čítače/časovače 1 |

| TCNT1L | Obsah čítače/časovače 1 dolní byte |

| TCNT1H | Obsah čítače/časovače 1 horní byte |

| OCR1AL | Komparační registr A čítače/časovače 1 dolní byte |

| OCR1AH | Komparační registr A čítače/časovače 1 horní byte |

| OCR1BL | Komparační registr B čítače/časovače 1 dolní byte |

| OCR1BH | Komparační registr B čítače/časovače 1 horní byte |

| ICR1L | Záchytný registr čítače/časovače 1 dolní byte |

| ICR1H | Záchytný registr čítače/časovače 1 horní byte |

| TCCR2 | Řídící registr čítače/časovače 2 |

| TCNT2 | Obsah čítače/časovače 2 |

| OCR2 | Komparační registr čítače/časovače 2 |

| OCDR | Komunikační registr pro podporu ladění přímo na čipu |

| WDTCR | Řídící registr WDT |

| SFIOR | Registr speciálních funkcí pro vstupy a výstupy |

| EEARL | Adresový registr EEPROM dolní byte |

| EEARH | Adresový registr EEPROM horní byte |

| EEDR | Datový registr EEPROM |

| EECR | Řídící registr EEPROM |

| SPDR | Datový registr SPI |

| SPSR | Stavový registr SPI |

| SPCR | Řídící registr SPI |

| OSCCAL | Registr pro kalibraci vnitřního oscilátoru RC |

| ACSR | Řídící a stavový registr analogového komparátoru |

| ADMUX | Řídící registr multiplexeru A/D převodníku |

| ADCSRA | Řídící a stavový registr A/D převodníku |

| ADCL | Datový registr A/D převodníku dolní byte |

| ADCH | Datový registr A/D převodníku horní byte |

| TWCR | Řídící registr TWI rozhraní |

| TWDR | Datový registr TWI rozhraní |

| TWAR | Adresový registr TWI rozhraní |

| TWSR | Stavový registr TWI rozhraní |

| TWBR | Registr přenosové rychlosti TWI rozhraní |

| GICR | Řídící registr přerušovacího systému |

| GIFR | Stavový registr přerušovacího systému |

| SPMCR | Řídící registr pro zápis do programové paměti FLASCH |

| UDR | Datový registr USART |

| UCSRA | Řídící/stavový registr A USART |

| UCSRB | Řídící/stavový registr B USART |

| UCSRC | Řídící/stavový registr C USART |

| UBBRL | Registr přenosové rychlosti USART dolní byte |

| UBBRH | Registr přenosové rychlosti USART horní byte |

| PORTA | Výstupní datový registr portu A |

| DDRA | Směrový registr portu A |

| PINA | Vstupní datový registr portu A |

| PORTB | Výstupní datový registr portu B |

| DDRB | Směrový registr portu B |

| PINB | Vstupní datový registr portu B |

| PORTC | Výstupní datový registr portu C |

| DDRC | Směrový registr portu C |

| PINC | Vstupní datový registr portu C |

| PORTD | Výstupní datový registr portu D |

| DDRD | Směrový registr portu D |

| PIND | Vstupní datový registr portu D |

Interní datová paměť SRAM

Slouží k ukládání dat nad rámec úložné kapacity pole pracovních registrů. Nejvyšší pracovní oblast datové paměti může být vyhrazena pro funkci zásobníku. Adresní prostor je vyhrazený od adresy 0x60.

- HRBÁČEK, Jiří. Komunikace mikrokontroléru s okolím. 1. vyd. Praha: BEN - technická literatura, 1999, 159 s. ISBN 80-86056-42-21.

- MATOUŠEK, David. Práce s mikrokontroléry ATMEL AVR ATmega16. 1. vyd. Praha: BEN - technická literatura, 2006, 319 s. μC. ISBN 80-730-0174-8.

- VÁŇA, Vladimír. Mikrokontroléry ATMEL AVR: programování v jazyce C : popis a práce ve vývojovém prostředí CodeVisionAVR C. 1. vyd. Praha: BEN - technická literatura, 2003, 215 s. ISBN 80-730-0102-0.

Obrázky a tabulky

- Obr. 1: [online]. [cit. 2015-01-30]. Dostupné z: http://www.atmel.com/images/doc2503.pdf

- Tab. 1: [online]. [cit. 2015-01-30]. Dostupné z: http://www.atmel.com/images/doc2503.pdf

Mikrořadiče AVR mají paměť RAM rozdělenou na:

- pole pracovních registrů, které jsou označené od R0 do R31;

- pole speciálních funkčních registrů (též označovaných Input/Output), pro které je v paněti RAM vyčleněno 64 adres ( tj. 0x3F);

- od absolutní adresy 0x0060 je pole interní datové paměti SRAM.