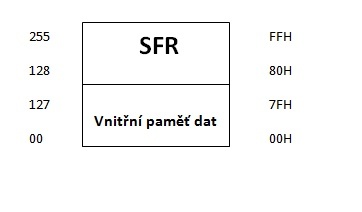

Vnitřní paměť dat má u základního typu 8051 velikost 128 bytů a tvoří ji (bráno zdola, tedy od adresy 00H) čtyři banky, z nichž každá má po osmi registrech (vždy R0 až R7). Registry z neaktivní banky nelze adresovat symbolickým označením (R0, R1 - R7), ale pouze přímou adresou (absolutně). Za nimi následuje tzv. bitová oblast. Pro ni je vyhrazeno 16 bytů na adresách 20H až 2FH. Bity z této oblasti jsou přímo adresovatelné (tzn. lze adresovat jednotlivé bity). V oblasti od 30H do 7FH se nachází zbývající vnitřní paměť a tu lze adresovat pouze po bytech (přímé i nepřímé adresování). Nad touto oblastí, tedy na adresách 80H až FFH, se nacházejí registry speciálních funkcí (SFR).

Paměť dat (Data Memory) může být až 64 kB.

Vnější paměť dat se používá při provádění instrukce MOVX, z toho je 256 B uvnitř čipu (vnitřní paměť dat).

Vnitřní paměť dat (je tvořena 256 B) se dělí na dolní a horní polovinu po 128 B.

V dolní polovině paměti dat (0-127) jsou umístěny:

4 registrové banky RB0-RB3, v každé registrové bance je umístěno 8 registrů R0- R7. Při inicializaci systému se nastaví sama banka RB0; registrové banky zabírají 32 B.

16 B bitově adresovatelného prostoru s jednotlivými bity mohu pracovat samostatně (Booleovský procesor), je tam tedy 16 x 8 =128 bitů.

volný uživatelský prostor - zbývající část do 128 B.

V horní polovině paměti dat (128 – 255) je umístěno 20 (21) SFR (speciálně funkčních registrů).

Obr. 1: Mapa paměti dat

Obr. 2: Podrobná mapa paměti dat

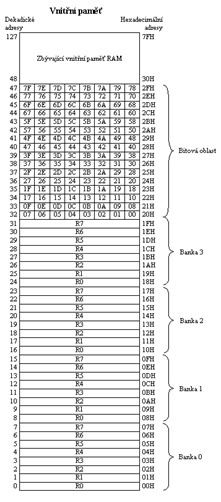

Mapa celé vnitřní paměti dat 0 – 255 (celkem 256 ) - podrobná

Paměť dat - dolní polovina

Mapa dolní poloviny paměti dat 0 – 127 (celkem 128 B).

Mapa dolní poloviny vnitřní paměti dat 0 – 127 (celkem 128 B).

Paměť dat - horní polovina

Horní polovina obsahuje 20 nebo 21 speciálních funkčních registrů. Registr DPTR je 16-bitový a v některé literatuře se používá celý nebo je rozdělěný na DPH a DPL – potom se uvádí 21 SFR. SFR (Special Function Registers - speciální funkční registry) slouží k nastavování a řízení činnosti 8051.

V další části jsou jednotlivé registry popsány. Hvězdičkou jsou vyznačeny bitově adresovatelné registry (lze adresovat po bitu)

- *Acc E0H Akumulátor, střadač, hlavní registr procesoru

- *B F0H registr B, registr pro dělení a násobení

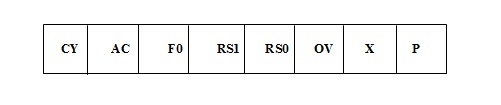

- *PSW D0H Program Status Word - stavové slovo programu, obsahuje informace o stavu programu (8 bitů, jeden bit je neobsazený).

Obr. 3: Registr PSW

Význam jednotlivých bitů :

- bit PSW.7 CY - příznak přenosu (Carry flag), je nulován nebo nastavován pomocí hardware či software během několika aritmetických a logických instrukcí (je to přenos přes osmý bit)

- bit PSW.6 AC - příznak pomocného přenosu (Auxiliary Carry flag), přenos z dolní poloviny bytu do horní poloviny bytu

- bit PSW.5 F0 - příznak nuly, je nastavován či nulován pomocí software jako uživatelem definovaný stavový příznak

-

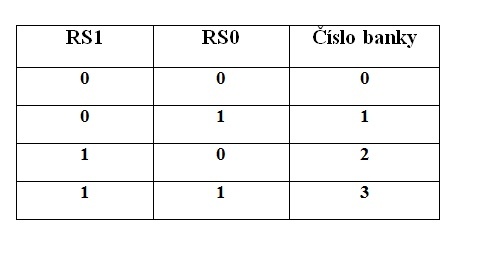

bit PSW.4 RS1

-

bit PSW.3 RS0 - bity pro nastavení registrové banky, binární kombinací těchto bitů se nastaví registrová banka, při inicializaci se nastaví RS0

Obr. 4: Nastavení registrových banak

- bit PSW.2 - OV, příznak přeplnění (Overflow flag), je nastavován/nulován díky hardware během aritmetických instrukcí k indikaci přetečení

-

bit PSW.1 - neobsazen (nezapojen)

-

bit PSW.0 - P příznak parity (Parity flag), je nastavován/nulován díky hardwaru v každém instrukčním cyklu. Tento bit indikuje sudou paritu obsahu akumulátoru, tzn. sudý počet jedničkových bitů.

Speciální funkční registr PSW – rozložení jednotlivých bitů.

SP 81H - Stack Pointer (ukazatel zásobníku) je 8-bitový registr. Je inkrementován před tím, než se uloží data při provádění instrukcí PUSH a CALL.

Po nulování (resetu) je SP nastaven na adresu 07 H, což znamená, že zásobník začíná na adrese 08H.

Jinak může být vlastní zásobník umístěn kdekoliv v rezidentní paměti RAM.

DPTR 82H - Data Pointer, ukazatel dat - základní funkcí ukazatele dat je uchovat 16-bitovou adresu.

Skládá se z horního bytu DPH a spodního bytu DPL. S ukazatelem dat můžeme pracovat jako s 16-bitovými registry nebo dvěma nezávislými 8-bitovými registry.

- *P0 80H Port kanály P0 - P3; tyto SFR jsou záchytnými registry kanálů 0-3

- *P1 90H

- *P2 A0H

- *P3 B0H

- *IP0 B8H Interrupt Priority Control - řízení priority přerušení

- *IE0 A8H Interrupt Enable Control - řízení povolení přerušení

- TMOD 89H Timer Mode Control - řízení režimu časovače/čítače

- *TCON 88H Timer Control - řízení časovače/čítače

- TH0 8CH Timer High č/č 0 (vyšší byt) regist. čítačů/časovačů

- TL0 8AH Timer Low č/č 0 (nižší byt)

- TH1 8DH Timer High č/č 1 (vyšší byt)

- TL1 8BH Timer Low č/č 1 (nižšší byt)

- *SCON 98H Seriál Control - řízení sériového kanálu

- SBUF 99H Seriál Data Buffer - buffer sériových dat SBUF se skládá ze dvou oddělených registrů. Z vysílacího bufferu (transmit buffer) a přijímacího bufferu (receive buffer). Když jsou data zapsána do SBUF, jsou umístěna do vysílacího bufferu, kde jsou uchována pro pozdější sériový přenos.

- PCON 87H Power Control - řízení napájení.